# **Chinese VLBI Data Acquisition System**

Rongbing,Zhao

CDAS is FPGA based VLBI data acquisition system . There are four IF inputs in CDAS. Each IF input could be 50 ~ 1024MHz frequency range. CDAS selects 50 ~ 512MHz or 512 ~ 1024MHz signal as exactly used signal to do processing. For 512MHz bandwidth signal, CDAS could extract up to 32 sub-channel data streams with different bandwidth, different central frequency and different output bit length. With these feasibilities, such as broad bandwidth input, flexible band central frequency choosing and convenient band width selection, multi-bits data streams output, CDAS provides major improvement feasibility for CVN observations. The main parameters of CDAS are described in Table

# Parameters of CDAS

| Parameters                      | Value                                          |  |  |  |

|---------------------------------|------------------------------------------------|--|--|--|

| IF input frequency              | 50 ~ 1024MHz 512MHz/512~1024MHz/<br>10~1024MHz |  |  |  |

| IF channels                     | Up to 4                                        |  |  |  |

| IF input power level            | -44~ -4 dBm                                    |  |  |  |

| IF sample rate                  | 1024Msps                                       |  |  |  |

| Reference frequency             | 5MHz                                           |  |  |  |

| Reference frequency power level | 7 ~ 13 dBm                                     |  |  |  |

| Base band channels              | Up to 32                                       |  |  |  |

| Base band frequency resolution  | 10 KHz                                         |  |  |  |

| Base band bandwidth             | 0.5,1,2, 4, 8, 16, 32MHz                       |  |  |  |

| Base band sample bit            | 1,2,4,8 bits                                   |  |  |  |

# **System Structure and Configuration**

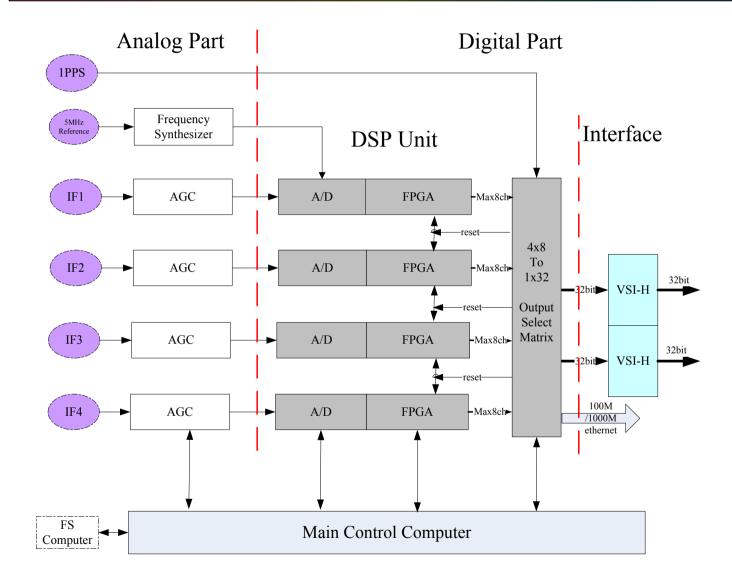

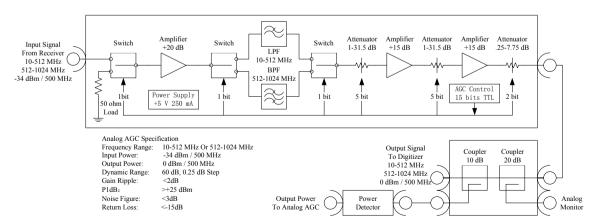

Figure shows the overview of CDAS System. Via AGC module, the amplitude of IF input signal will be stepped control to suit the ADC requirement. Under the control of the command of CDAS, low or high IF signal could be selected to process. The maxim dynamical rang of amplitude is 60dB with minimum delay change during the amplitude adjusting. The main control computer which belongs to the digital part is responsible for the whole system communicating with Field System (FS) computer, command the system and diagnostic the status of CDAS during the observation time.

Like most other digital VLBI data acquisition system , approach to 'ADC + FPGA' is adopted for CDAS which composed of analogy part and digital part. The analogy part is responsible for anti-aliasing and AGC (Automatic Gain Control) which has about more than 40dB dynamic range of input power level from -44dBm to -4dBm in order to fitting for tracking spacecraft and keep the optimal quantization level for the following ADC.

#### **System Structure and Configuration**

The CDAS analogy part consists of four AGC modules, one system clock generator and one control module. Each module is integrated in an individual box, which has perfect EMC characteristics. All of such modules are installed in a 19 inches chassis with power supply. Figure 2 and Figure 3 show the pictures of analogy part and digital part of CDAS separately. The digital part is responsible for data acquisition and process. The main hardware of digital part is two PCB boards which are developed by SHAO. One of these two PCB boards is an interface board. This board has a VSI-H interface which can be connected with MK5B recorder. Another of these two PCB boards is so named DSP unit which included two channel 1Gsps Analog to Digital convertor and four large scale FPGAs in daisy chain. The digitizing of each IF signal and processing the signal is completed in real time in this DSP board. The signal processing are including Direct Digital Frequency Synthesis (DDS), digital down convert, filters and power level calculating etc. Each DSP board could process one IF input signal.

### **System Structure and Configuration**

Each FPGA on the DSP board could produce one BBC including both USB and LSB. The output data length of BBC is 8 bits. There are four DSP boards in CDAS which are used to processing four IF input signals. The output results of these four DSP boards would be sent to an output select unit which includes a 128 to 32 cross switch and re-quantification module. According the command of CDAS, the quantification module will determine the output bits number of sub-channels. The output bits number could be from 1 to 8 bits. On the basis of the command of CDAS, via cross switch, the system could select required sub-channels in required order to compatible to different VLBI data format. Such sub-channel data streams could be sent to Mark 5B system via interface board.

Figure 5 shows the photo of DSP board. This is a 6U standard Europe PCB board with c-PCI interface. There are one ADC (AT84AD001B, dual 8-bit analog –to-digital converter, Atmel) and five FPGAs on the board.

# Analog AGC Module

Figure shows the diagram of AGC module. The CDAS could be used to observe radio source and spacecraft. The signal power of spacecraft has large dynamic range during they go away from earth to deep space. Automatic gain control (AGC) is necessary for station receiver and backend system. Normally, it should be an adaptive <u>system</u>. The average output signal level could be <u>fed back</u> to adjust the <u>gain</u> to an appropriate level for a range of input signal levels. The system delay will be changed following the value of fed back. Concerning to reduce the variance of system delay and phase during target signal changing, the 'amplify + <u>attenuator</u>' combinations are used for system gain control. The advantage of this combination could be maxim reduce the change of system delay. We used three amplifies, one has 20 dB gain and two has 15 dB gain each, and three adjustable attenuators with 60dB total decrement. There are a network which is configured with two microwave switchers, one low pass filter and one band pass filter. The function of this network is selecting low or high IF signal to process by command. The same delay values are also required for low and high pass. Figure 6 shows the curves of Gain / Frequency characteristics of four AGC modules in lower IF mode. Under the control of the command of CDAS, it could select low or high IF signal to process. Via AGC module, the amplitude of IF input signal will be stepped control to suit the ADC requirement. The maxim dynamical rang of amplitude could be 60dB with minimum delay change during the amplitude adjusting.

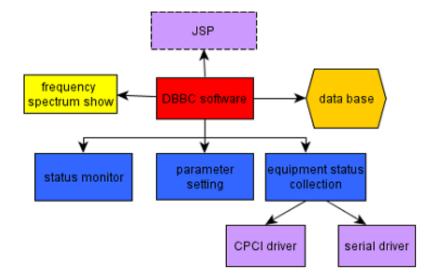

The software can control digital converter, AGC and output of CDAS and monitor their status based on the user command. Furthermore, the software also receives the command from FS system and transfer the status of CDAS to the FS.

#### **CDAS Control Software**

The main Applications Places System @@ 🗉 🖔 16:33 🚯 digital age \_ O X - 0 × message show 5 monitor its upshift downshift upthreships :\* upower dapower demax U DITTRO 10:24:30:10:24:30:is loading ! 17896L 2074 10:24:57:10:24:57:Done is high No CRC erro.system is working normally! 1.74577 2223 0 389 There are 179054 174579 2158 2114 389 10:24:58:a/d sreset success 10:24:58::reset synboard bbc3 178925 176609 2223 2074 389 0 0 10:25:04:32m reset success 179041 174570 2234 2150 389 status shc 10:25:04: reset synboard bbc5 149142 147880 1977 2007 355 10:25:06:filter sreset success 149225 147961 1942 1094 0 . 355 10:25:06 reset synhoard plot. The r bbc7 149139 147944 1.962 1949 0 0 355 10:25:57:10:25:57:is loading bbcB 14909.6 147895 1961 2021 FPGA Setting mally 216558 213130 2411 2450 bbc9 .6lm.7ls.7lm.8ls.8lm.1us.1um.8u Clear 40 Plag bbc10 216664 213247 2227 2265 U/LSB Band widthBitWidthFrequency StartPhase us 14um Clear AD bbc11 0 216399 213115 2295 2298 13us,13um,14us,14um,15us,15u ÷ 0.00 ÷ Set1 1 < 606.990000</li> USB v 2m 2310 bbc12 0 216518 213241 2450 \$ls.14lm.15ls.15lm.16ls.16lm bbc13 0 101504 177265 21.29 2103 Lond Sittile USB - 2m 1 - 606.990000 0.00 + Set2 Set All BBC 1 - 606.990000 USB - 2m 0.00 - 5et3 6 Load All File Edit View Configure Tool About USB v 2m - 1 606.990000 - 0.00 - Set4 Lad Board1 USB · 2m - 1 606.990000 ÷ 0.00 ÷ Set5 Lad Board2 ock/ulpci atten H/Low ac Lad Board3 1 - 606.990000 IFA lock 6.00 HRASS .... USB - 2m 0.00 5et6 💽 ifb IFB lock 6.00 HPASS Lad Board4 ..... ÷ 0.00 ÷ USB v 2m - 1 606.990000 Set7 IFC lock 27.00 HPASS m HPASS IFD lock 27.00 rma Reset USB • 2m - 1 606.990000 0.00 - Set8 DDSReset Set9 Cal USB • 2m - 1 606.990000 ÷ 0.00 ÷ ADReset 16um USB v 2m 1 < 606.990000</li> ÷ 0.00 ÷ Set10 32MReset Load1 USB • 2m - 1 606.990000 0.00 - Set11 FilterReset QueryL QueryAll Auto 韋 Load2 ResetAll USB • 2m - 1 • 606.990000 0.00 - Set12 LogToFile Test USB v 2m 1

606.990000 ÷ 0.00 ÷ Set13 fleset the syn board-Reset USB - 2m 1 - 606.990000 - 0.00 - Set14 606.990000 USB • 2m - 1 0.00 Set15 VD overflow time-606.990000 USB v 2m - 1 0 AD Set 10-11-01-00+ DD011-0-000001000-73000010111 10:27:34:Set BBC15:0.000000,606.990000,0,4,0 10:27:34>Set BBC16:0.000000,606.990000,0,4,0 10:27:35:dds reset success 10:27:35::reset symboard 10:32:55:DBBC board 1 A/D\_I overflow(one time)! 10:52:10:DBBC board 0 A/D I overflow(one time)! 🔿 😽 message show 🕤 🕤 digital agc S DBBC Control FPGA Setting [dbbc correlator plot ]

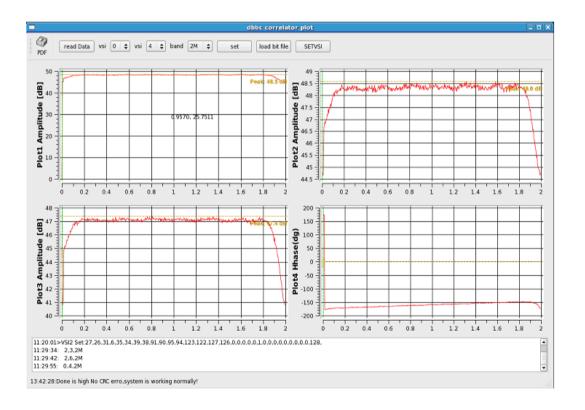

### **Software Spectrum Monitor**

You can select two channels data to plot the autocorrelations and cross-correlation including amplitude and phase (see Figure). In the plot window, the figures show the autocorrelation of channel 1 and 2 and w the amplitude and phase of cross correlation.

We modified the drudg software ,add the cdas rack to support the CDAS mode setting.

- 1.Add the the 64mhz external frequency support

- 2.Support the receiver high Lo and Low Lo mode

- 3.Add new mode vlba\_c

# **Cross Switch**

| BS | vlba    | vlba_c |      |                |     |            |     |

|----|---------|--------|------|----------------|-----|------------|-----|

|    | FS/DBBC | FS     | DBBC | 16             | 1LS | 1LS        | 1LS |

| 0  | 1US     | 1US    | 1US  | 17             | 1LM | 1LM        | 1LM |

| 1  | 1UM     | 1UM    | 1UM  | 18             | 2LS | 2LS        | 5LS |

| 2  | 2US     | 2US    | 5US  | 19             | 2LM | 2LM        | 5LM |

| 3  | 2UM     | 2UM    | 5UM  | 20             | 3LS | 3LS        | 2LS |

| 4  | 3US     | 3US    | 2US  | 21             | 3LM | 3LM        | 2LM |

| 5  | 3UM     | 3UM    | 2UM  | 22             | 4LS | 4LS        | 6LS |

| 6  | 4US     | 4US    | 6US  | 23             | 4LM | 4LM        | 6LM |

| 7  | 4UM     | 4UM    | 6UM  | $\frac{1}{24}$ | 5LS | 5LS        | 3LS |

| 8  | 5US     | 5US    | 3US  | 25             | 5LD | 5LD<br>5LM | 3UM |

| 9  | 5UM     | 5UM    | 3UM  |                |     | _          |     |

| 10 | 6US     | 6US    | 7US  | 26             | 6LS | 6LS        | 7US |

| 11 | 6UM     | 6UM    | 7UM  | 27             | 6LM | 6LM        | 7UM |

| 12 | 7US     | 7US    | 4US  | 28             | 7LS | 7LS        | 4US |

| 13 | 7UM     | 7UM    | 4UM  | 29             | 7LM | 7LM        | 4UM |

| 14 | 8US     | 8US    | 8US  | 30             | 8LS | 8LS        | 8US |

| 15 | 8UM     | 8UM    | 8UM  | 31             | 8LM | 8LM        | 8UM |

### **CDAS Installation**

Since year 2009, CDAS has been equipped in Shanghai, Beijing, Kunming and Urumchi VLBI stationincludes of FS Computer, Mark5B, and a LCD monitor. After integration in station, the firmware and software of CDAS have been updated for several times to improve the performance and correct the bugs.