# UniBoard Rev 1.0 hardware point of view

## Work done since last meeting

- Optimize design for production

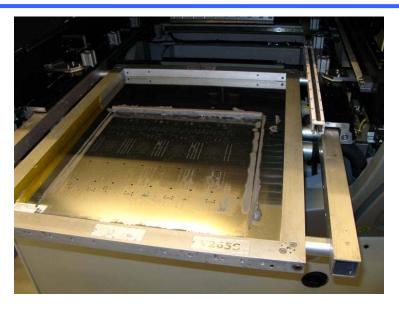

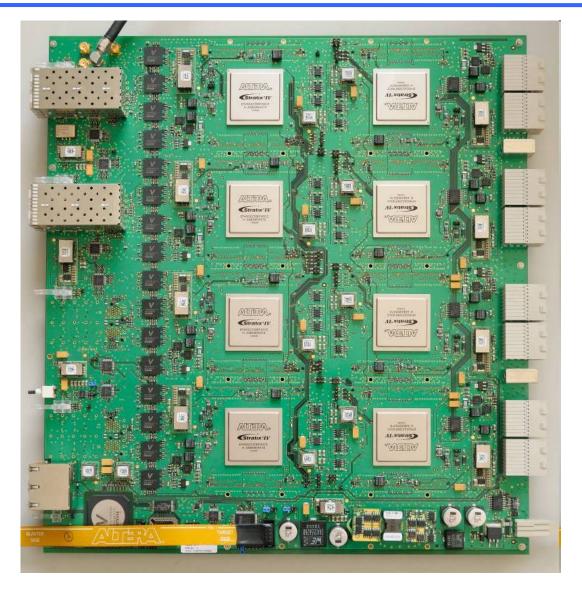

- Production of UniBoard (Neways)

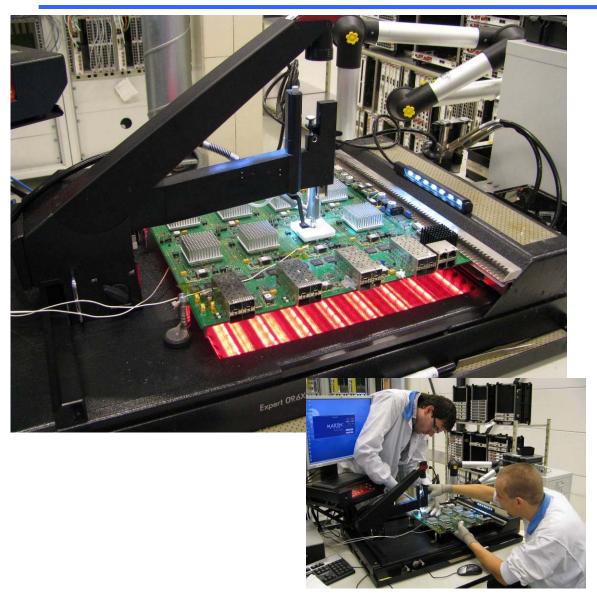

- Testing the board

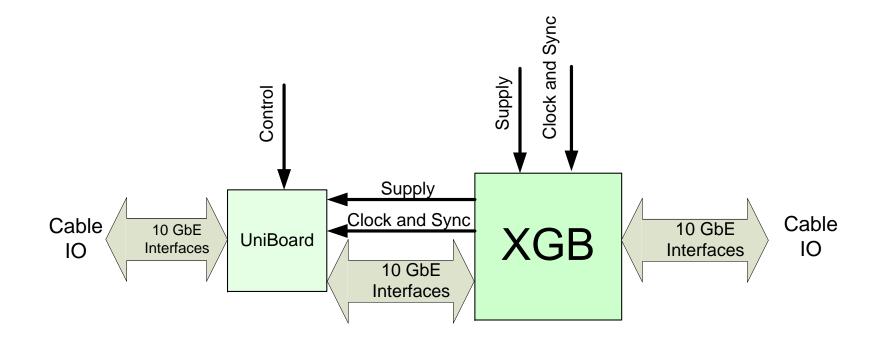

- ➤ Made 10G break out board (XGB)

- Design housing for UniBoard / XGB

- Memory and ADC test boards made

- Start with updating design for rev 2.0

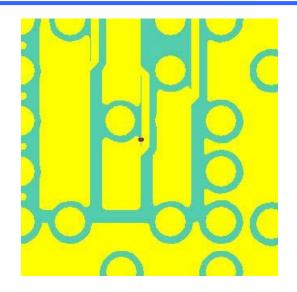

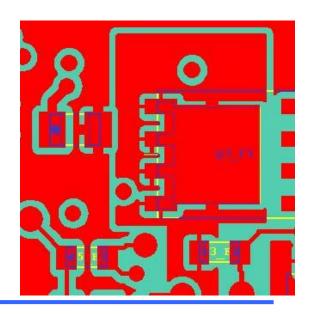

## Optimize design for production

## DFM for:

- Preventing PCB production errors

- Reducing assembly problems like:

- Wrong shapes

- tomb stones

## Result:

Only one wrong footprint (of 138 different parts)

## **UniBoard Production**

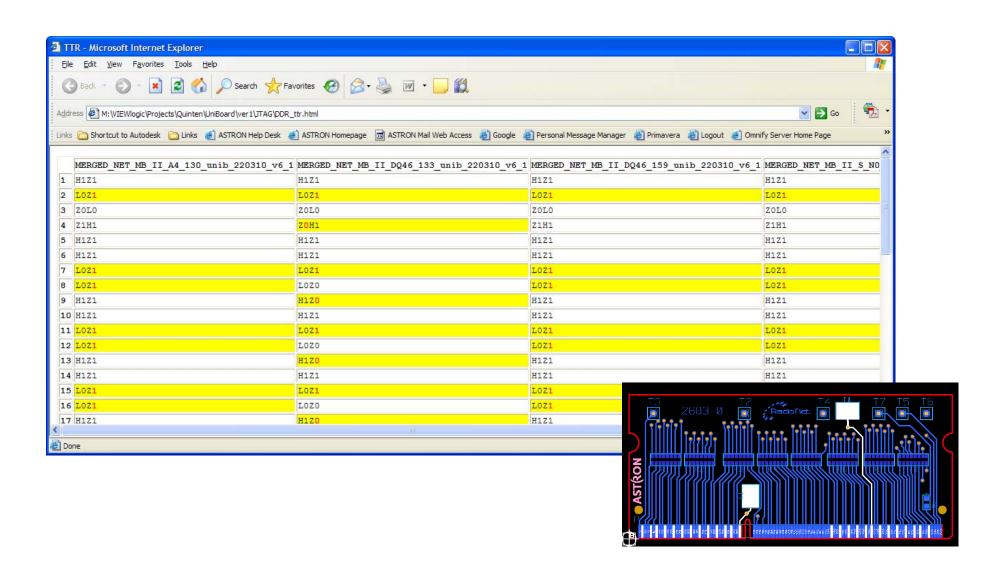

- Boundary scan

- > DDR3 tested up to 1033MT/s

- Inner FPGA interfaces tested up to 6.5Gbps

- ➤ IO interfaces tested up to 10Gbps with optical interfaces

- ➤ ADC interfaces tested up to 200MSPS (due to limited of test fixture)

- GbE control tested (unmanaged) hardware o.k. software need update.

- Small PCB issue's

- 1 shape

- Different values (termination and power settings)

- DDR3 power supply not capable of max. current

- Transceivers Power

- Not sufficient output power for direct attachment cabling

- Tx, Rx swap in SFP+ slot 3

- > FPGA

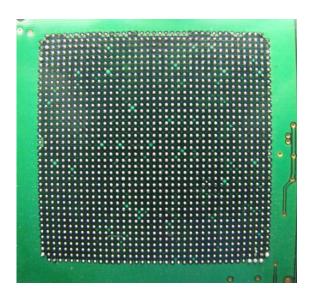

- DDR pinning lost connection

- Ethernet switch

- Memory size for managed switch

- More testing needed

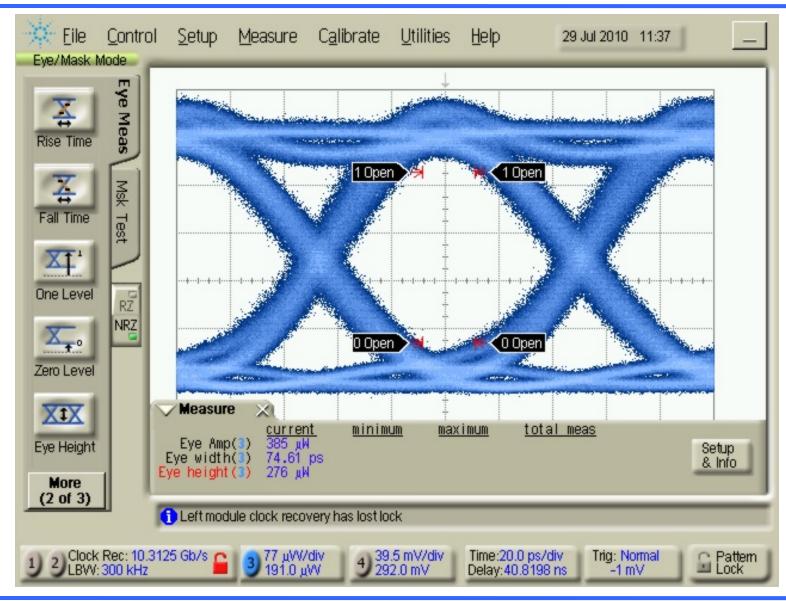

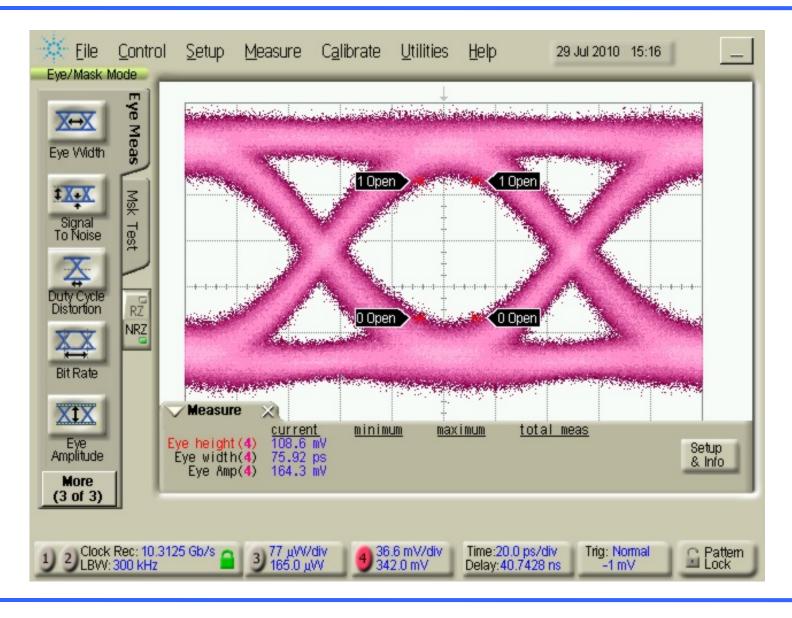

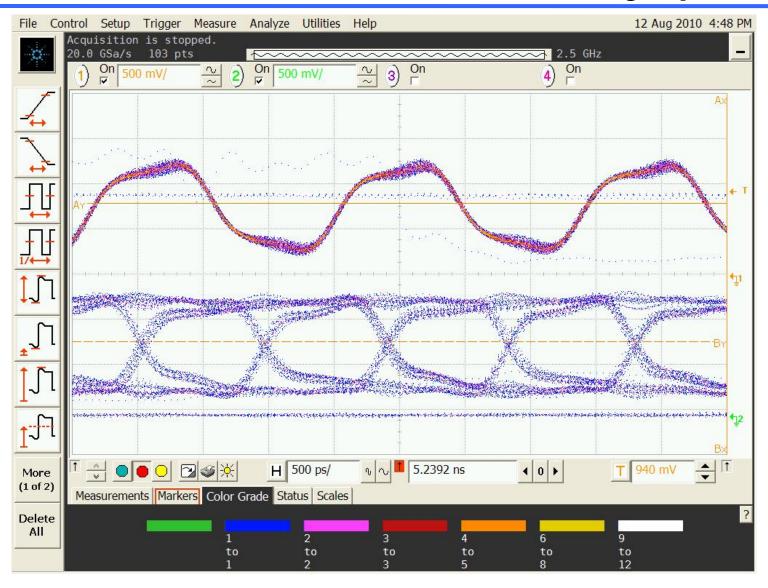

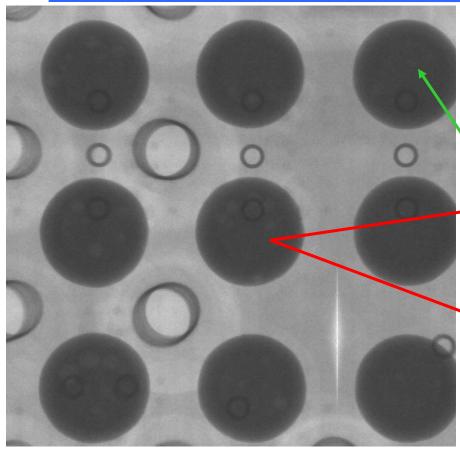

# ASTRON Redio Poptical Measurement results

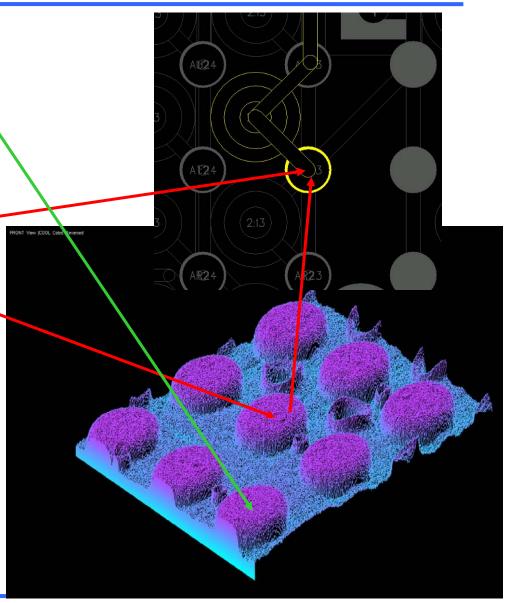

## DDR3 eye pattern

## X-Ray scan on memory lines

- ➤ BN 2 pin AT23

- > MBII A4

## Removing of FPGA

- DDR3 power supply (setting of the SMPS)

- Ethernet switch, unmanaged

- > Remove Tx Rx swap in SFP+

- Removing small errors

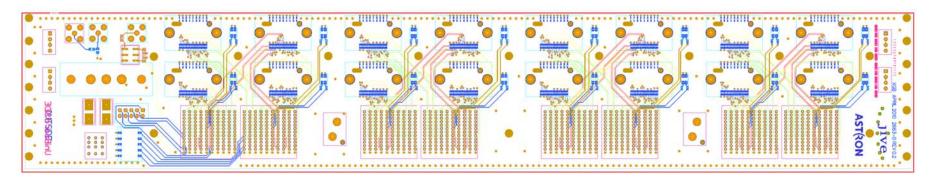

## XGB 10Gig Breakout board

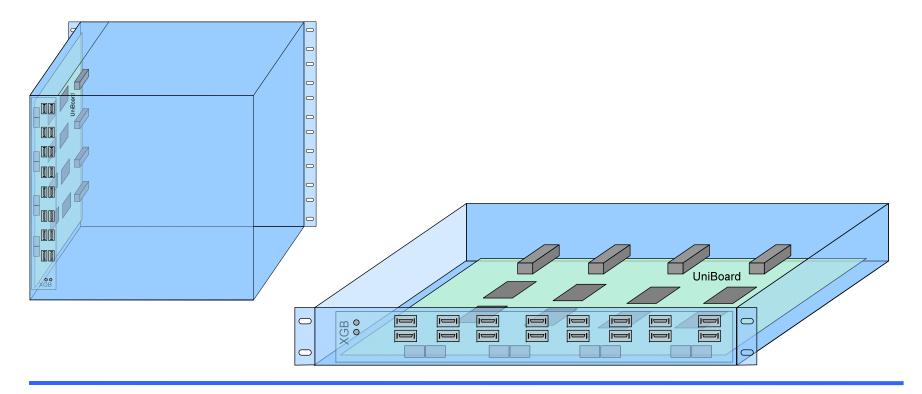

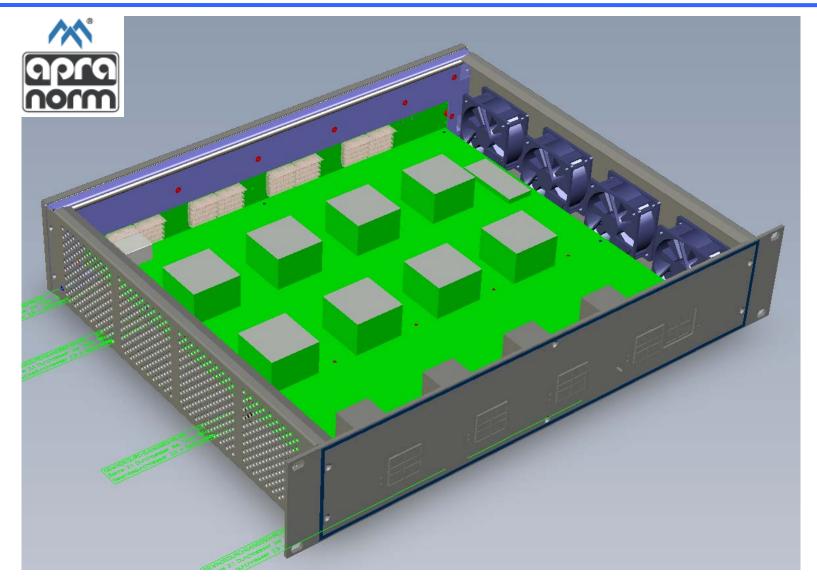

## UniBoard 2HE Housing

#### **Documentation**

#### Hardware

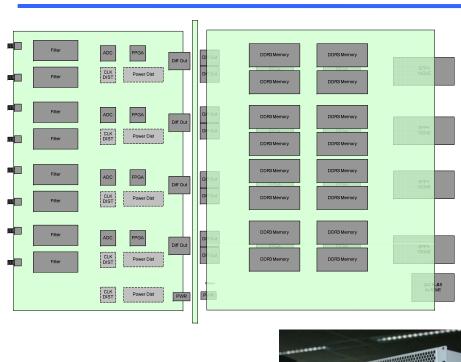

- \* UniBoard for EVN: Block diagram and analysis. Gijs Schoonderbeek, 13-3-2009

- \* MuniBoard hardware design. Gijs Schoonderbeek, Sjouke Zwier, 29-01-2010

- \* UniBoard Schematic. Gijs Schoonderbeek, Sjouke Zwier, 29-01-2010

- \* TPPT for Schematic Review. Gijs Schoonderbeek, Sjouke Zwier, 07-07-2009

- \* MuniBoard PCB (preplacement) Sjouke Zwier / Gijs Schoonderbeek. 15-09-2009

- \* TuniBoard Test Description. Sjouke Zwier / Gijs Schoonderbeek. 15-04-2010

- \* MuniBoard Board Description. Sjouke Zwier / Gijs Schoonderbeek. 14-07-2010

- \* XGB hardware design document. Gijs Schoonderbeek, Sjouke Zwier, 07-04-2010

- \* XGB Schematic. Sjouke Zwier / Gijs Schoonderbeek 14-04-2010

- \* XGB PCB Overview. Sjouke Zwier / Gijs Schoonderbeek 14-04-2010

- \* MuniBoard/XGB housing Sjouke Zwier / Gijs Schoonderbeek 07-07-2010

Description which tests will be done during production

Description of board, connectors and other non firmware issues

http://www.radionet-eu.org/fp7wiki/doku.php?id=jra:uniboard:documents

- Finalize Redesign

- Find cause of DDR connection problem

- Finish testing

- Remove errors in rev 1.0 (update started)

- Update XGB

- Start production UniBoard

- Start production of housing

- ➤ Prepare for production test

## Plans for UniBoard Rev 3.0

- Transceiver change to different type

- Backplane ON/OFF

## Subrack with ADC for Apertif

- 4 UniBoards

- ➤ 8 ADC-boards (ADU)

- ▶ 1 power and clock board (PAC)

- ▶ 1 backplane

## Astron UniBoard plans

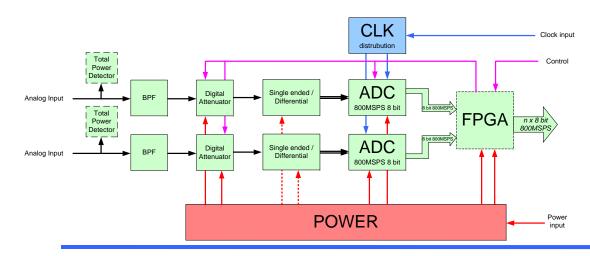

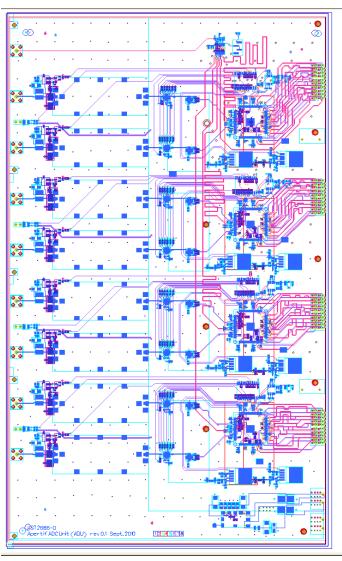

### **ADU**

- National Semiconductor ADC08D1200 800MSPS 8 bit

- > 8 channels per board

- > 400-800MHz filters

- Ready for power over coax

- > Est. < 1W / channel

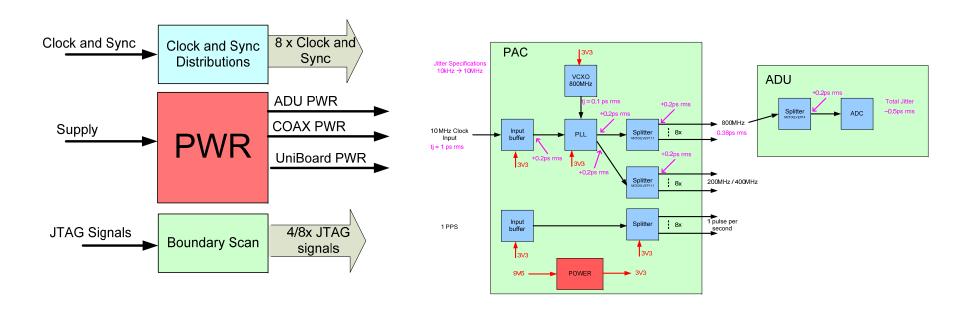

## PAC

- Clock distribution to ADCs and UniBoards

- Power distribution

- Boundary scan signal distribution

## Astron UniBoard plans

## Planning other boards

> Finish UniBoard and XGB

- > ADU current in production

- PAC specification finish design started

- ➤ Backplane Q1 2011 in production