### RadioNet FP7 Joint Research Activity

# The UniBoard

## Generic Hardware for Radio Astronomy Signal Processing

J. E. Hargreaves

Contract nr. 227290

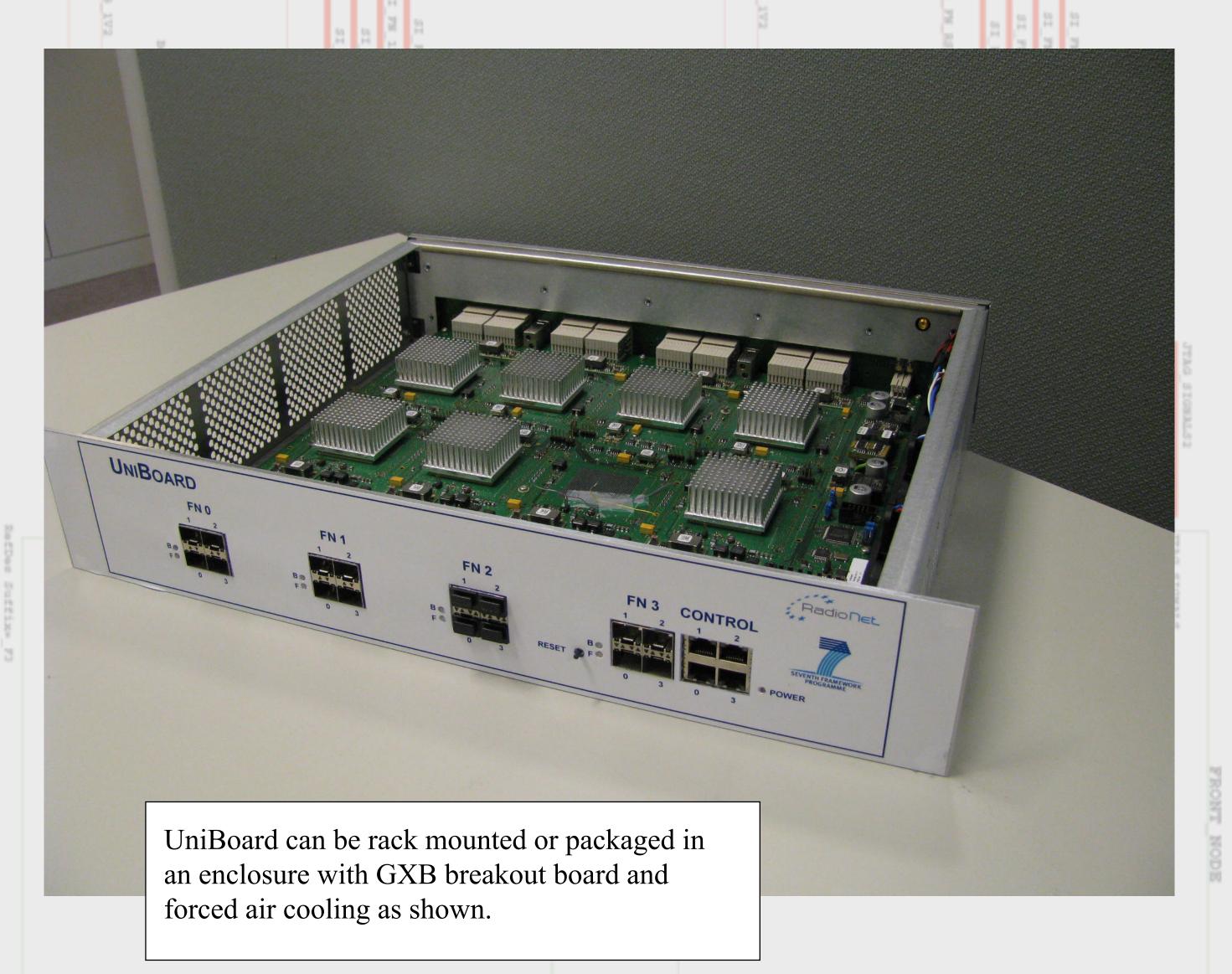

#### The Project:

Concentrate as much computing power and I/O as possible on a "reasonably" sized PCB Based on state-of-the-art FPGAs for best performance/shortest development time Take advantage of expertise at Astron obtained through Lofar development Keep board interfaces as generic as possible (1 and 10G Ethernet, DDR3 memory) Maximize project-wide re-use and exchange of VHDL code through a shared repository. Test bench for SKA instrumentation: several Tflops/board, power efficiency, volume 3-year project, started January 1 2009, funded by EC and participants (total of 1.4 Meuro)

#### The Hardware:

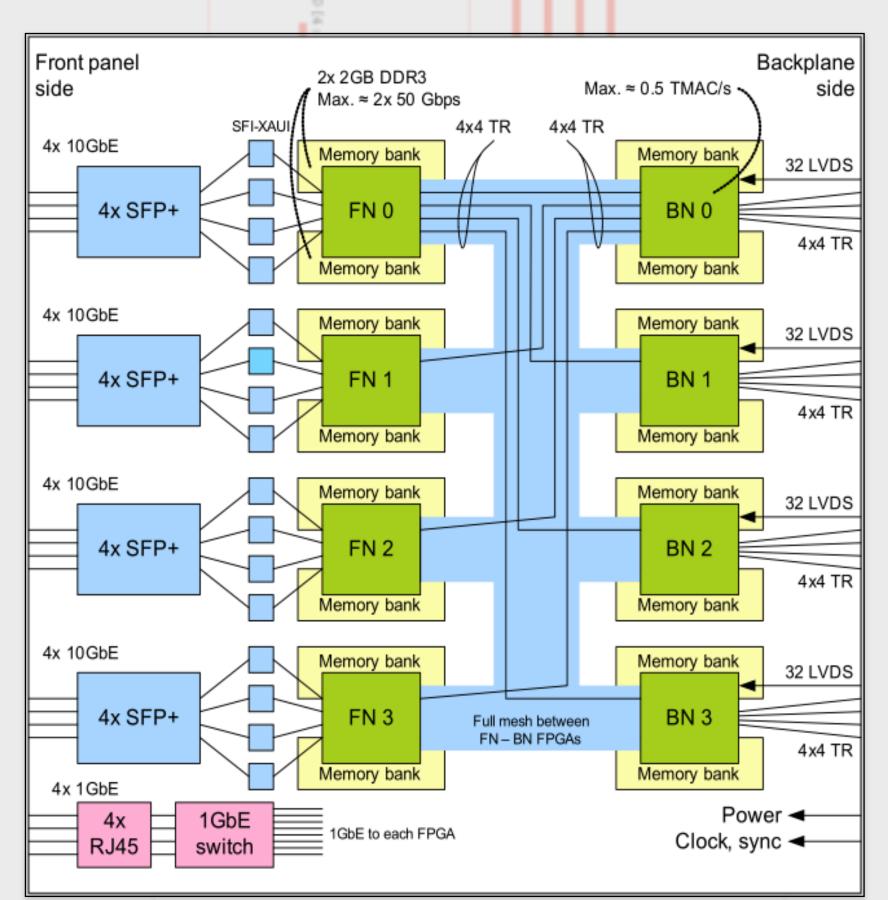

8 Altera Stratix IV 40nm FPGA, type EP4SGX230KF40C2, 1288 multipliers, 1517 pins

One front node → all back nodes bi-directional mesh

14 layers

8 × 2 DDR3 modules

24 10GbE ports 1GbE control link to each node

$4 \times 32$ -bit LVDS in

48V power supply

Estimated maximum power consumption 280 W

#### The Applications:

Correlators Beamformers

Digital receivers Pulsar binning machine

Pulsar Search

RFI Mitigation

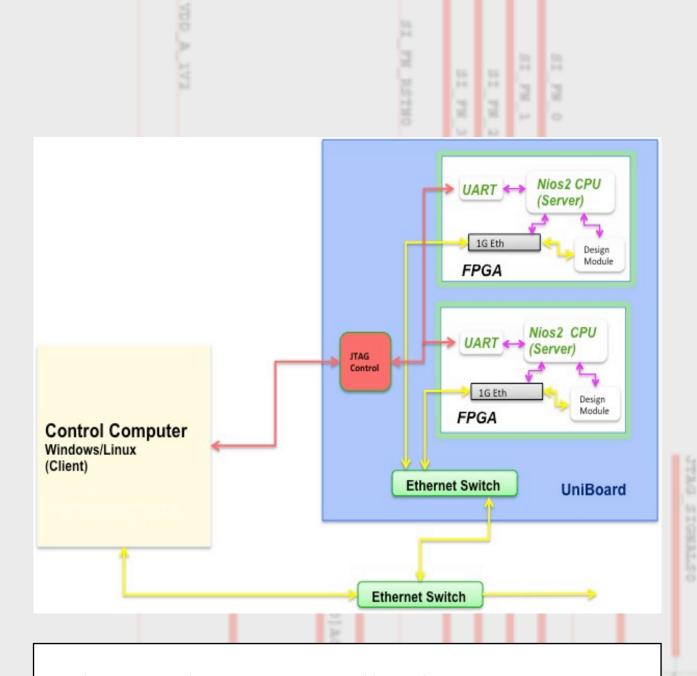

Above: Firmware applications are controlled over a 1GbE link using embedded soft processors in the FPGAs

Left: Block diagram of the UniBoard hardware

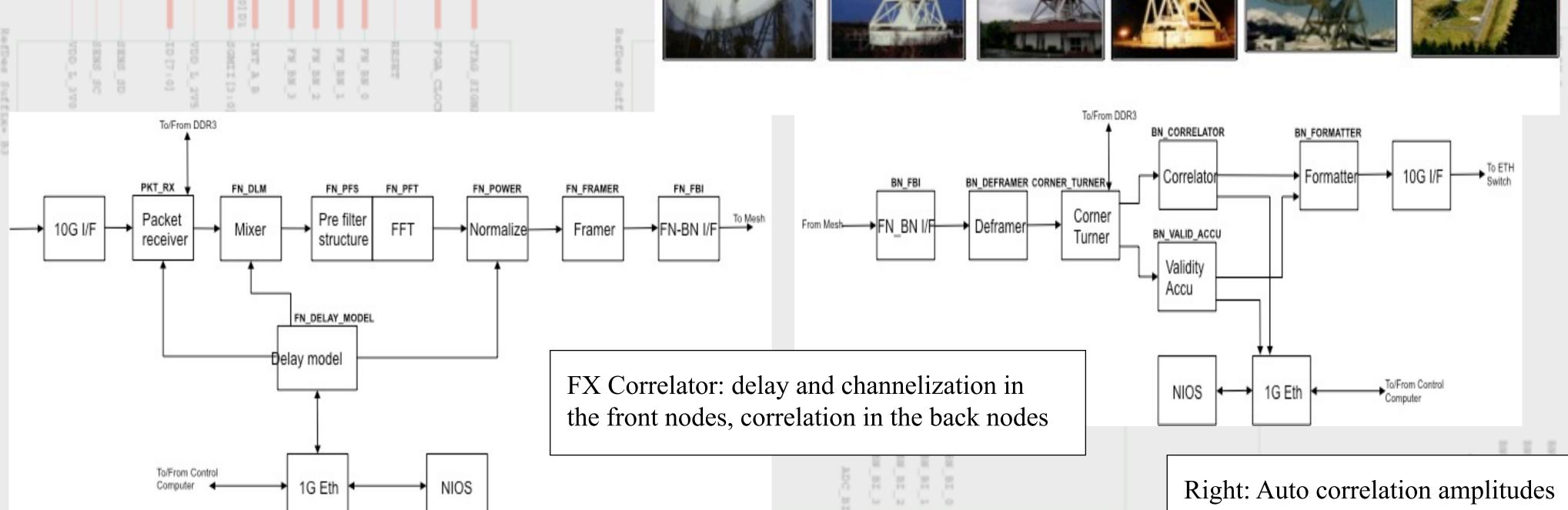

#### **EVN Correlator Specifications**

Input

Stations Polarizations 1-8bits Resolution

**VDIF** Format Sub-banding 1,2,4,8,16,32,64MHz Total Bandwidth 4096MHz

Further information: Jonathan Hargreaves, <a href="mailto:hargreaves@jive.nl">hargreaves@jive.nl</a>

**Processing**

Integration time Correlation products Spectral resolution

22ms - 1s2112 full stokes 15kHz

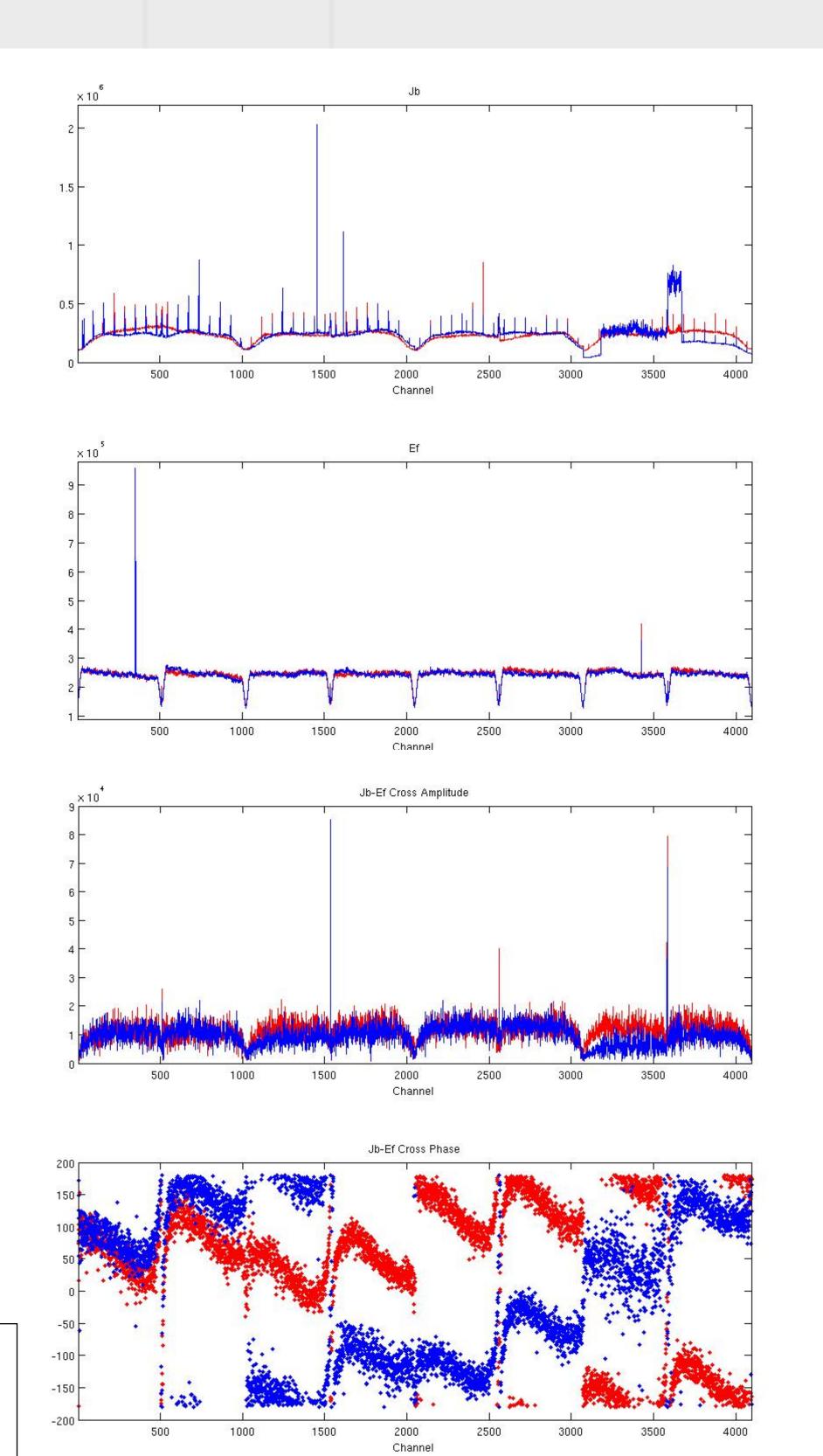

(top) and cross correlation amplitude and phase (bottom) for a single baseline, 0.25s integration